# **ULVAC IR Seminar 2025**

# Aiming for Further Growth in the Semiconductors and Electronics Field

October 3, 2025

#### Disclaimer regarding forward-looking statements etc.

#### Forward-looking statements

Forward-looking statements of the company in this presentation are based on information that was available at the time these documents were prepared. There are several factors that directly or indirectly impact the company performance, such as the global economy; market conditions for FPDs, semiconductor, electronic devices, and raw Materials; trends in capital expenditures and fluctuations in exchange rates. Please note that actual business results may differ significantly from these forecasts and future projections.

#### About This Document

Please note that this IR seminar material and presentation were not created for technical purposes and contain simplifications to facilitate investor understanding.

# **Growth Strategy**

# Selection and concentration of a business portfolio centered on semiconductors and electronics

- Accelerate focus on Semiconductors and Electronics

- Create new semiconductors and electronics-related businesses by leveraging synergies among businesses

- Expand business through M&A and other initiatives

# Approx. ¥110 billion increase

# **Today's Agenda**

Initiatives for Semiconductor Process Expansion

16:05-16:20 Tomoyasu Kondo, Senior Executive Officer,

General Manager of Semiconductor Equipment BU

New Initiatives in Advanced Packaging

16:20-16:35

Harunori Iwai, Senior Executive Officer

Junya Kubo, Sales Department 2

Semiconductor and Advanced Electronics Business HQ

3 Strengths of the Surface Analysis System and Future Developments

16:35-16:50

Hirohisa Takahashi, Executive Officer, President and CEO of ULVAC-PHI, Inc. Takuya Miyayama, Senior Manager, Product Strategy Department, ULVAC-PHI, Inc.

4 **Q&A** 16:50-17:10

# **Initiatives for Semiconductor Process Expansion**

Tomoyasu Kondo Senior Executive Officer, General Manager of Semiconductor Equipment BU

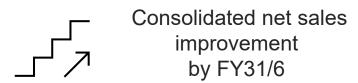

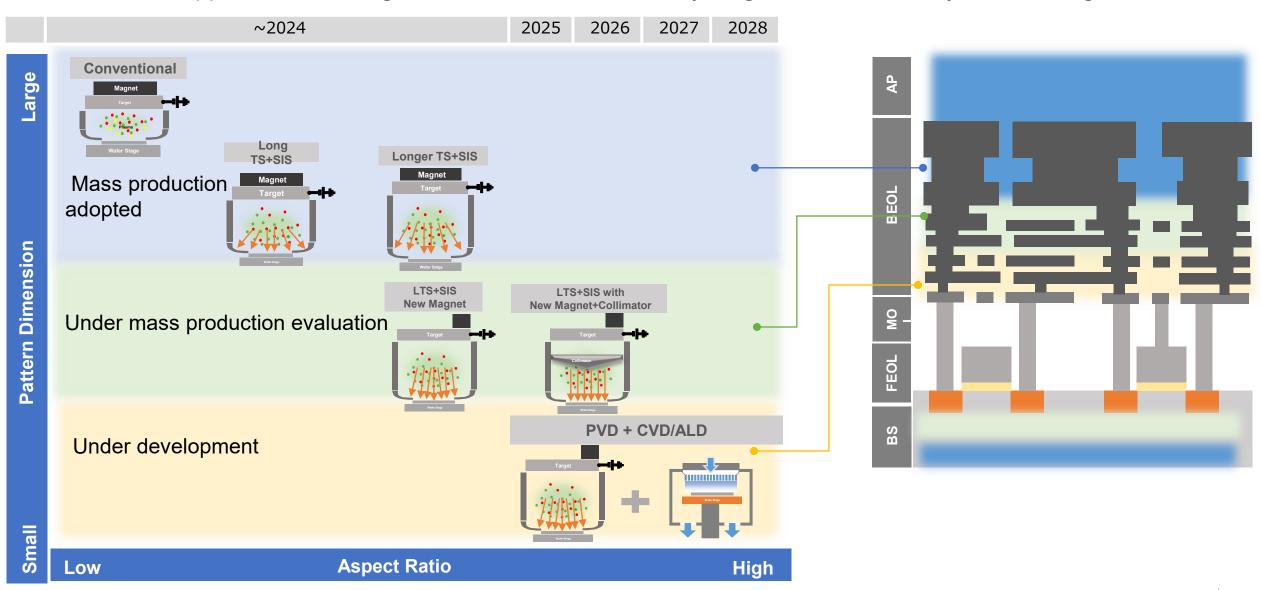

# **Advanced Logic Foundry Technology Roadmap**

- New Mid-to-Long-Term Management Plan Over the six years through FY31/6, the significant structural changes to semiconductor devices will occur

- >> Increased patterning steps and adoption of new materials will expand opportunities for our core PVD deposition processes

Source: Created based on Imec Roadmap

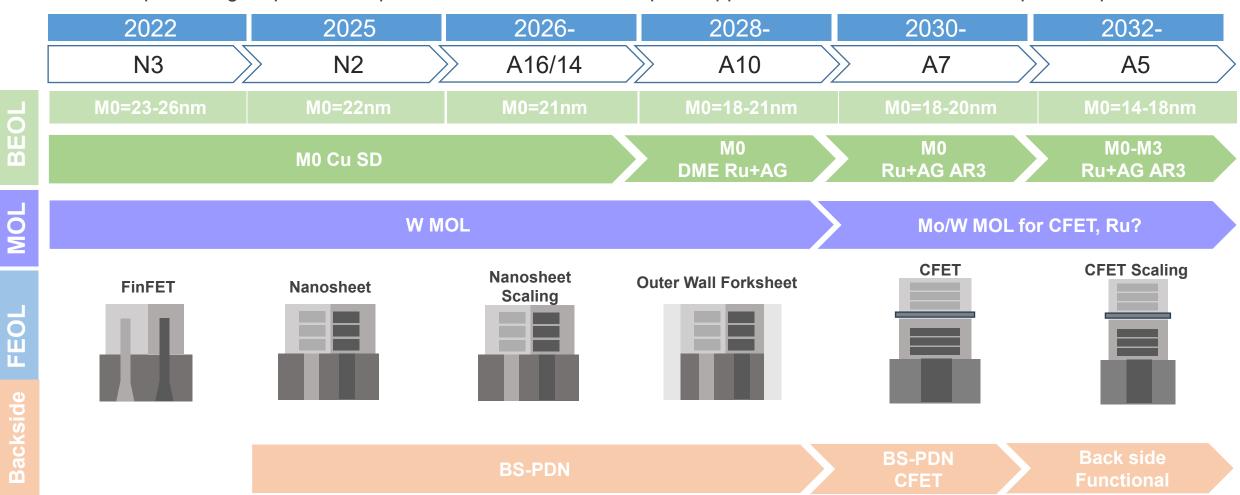

#### Our Hard Mask Process Expansion and Application to Other Processes

Spillover effects through securing mass production PORs with top customers

Technology application to other processes, process expansion

## **Our Advanced Semiconductor Development Framework**

Strengthening Advanced Semiconductor Device Development: In addition to opening the Technology Center Pyeongtaek (Korea), we have commenced participation in the Imec program in Belgium. We are building a development framework with a forward-looking perspective

Advanced Customer Development Base

Advanced Semiconductor Research Institutions (Participated in 2025)

Semiconductors and Electronics Technology Research Institute (Established in 1990)

Technology Center Pyeongtaek (Established in 2024)

| ~N+2                                  | N+2 to N+1            | N+1                                 | N                                                 |  |  |

|---------------------------------------|-----------------------|-------------------------------------|---------------------------------------------------|--|--|

| Advanced Technology Sensing           | Equipment Development | Customer JDP/JEP                    | Mass Production Feasibility and Yield Improvement |  |  |

| Development Collaboration             | Process Development   | Development POR/Mass Production POR | CS Support                                        |  |  |

| Early sensing for sufficient lead tir |                       |                                     | POR/Mass Production                               |  |  |

#### **Semiconductor & Logic Growth Roadmap**

#### **Technology Trends**

Progress in miniaturization

Introduction of new materials

#### **Our Strengths**

Stress control

Low-particle film deposition

Low-temperature film deposition technology

**■** Growth Roadmap

Expansion of new materials and low-resistance film deposition technologies

Low-resistance new materials

☆ Proven track record

Acquisition of advanced logic metal wiring processes

Cu interconnect

AI/W Process

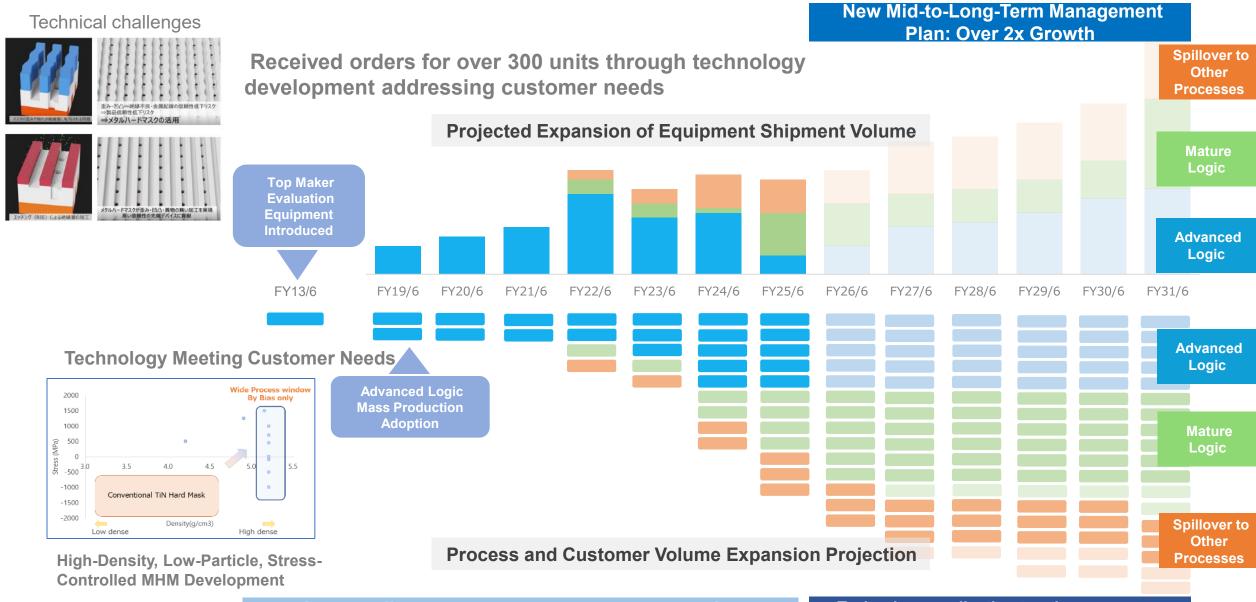

#### Hard mask technology development leveraging stress control and low-particle deposition

★ Hard masks for BEOL wiring formation

★Hard masks for GAA formation

Hard mask for back-side wiring formation

Customer Technology Roadmap

2024

2025

2026

2027

2028

2029

2030

2031

Logic

2nm

A14

A10

A7

# Mid- to Long-Term Goals

# Hard Mask PVD+ Securing market share through the capture of the metal wiring process

- Centering on metal hard mask technology, which is the de facto standard at 5 nm and 3 nm, we aim to establish a market share in hard mask applications and related process technologies.

- Aiming to enter and expand into the metal wiring process, where PVD is most widely used

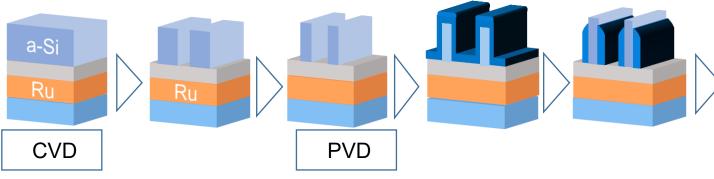

## An Example of Future Technology Development for Advanced Logic

#### **Example of hard mask applications in Ru DME processes**

Shape distortion during trimming Density, Si purity, low deposition Disadvantageous during pattern temperature, low outgassing transfer

⇒Superior resistance to pattern distortion and pattern transfer

Effective against microbridges and defects

#### **Amorphous Si: Comparison with PVD and CVD**

|                           | CVD               | PVD      |  |  |

|---------------------------|-------------------|----------|--|--|

| Deposition<br>Temperature | High              | Low      |  |  |

| Purity                    | Low               | High     |  |  |

| Impurities (Hydrogen)     | High              | None     |  |  |

| Hardness                  | Low               | Mid      |  |  |

| Film Thickness            | thick             | mid      |  |  |

| Patterning accuracy       | Bad               | Moderate |  |  |

| Temperature tolerance     | Moderate          | High     |  |  |

| Shape Retention           | Low               | Moderate |  |  |

| Film-forming particles    | Will be Evaluated |          |  |  |

|                           |                   |          |  |  |

# **Sputtering Technology for Metal Wiring Processes: Logic**

Increased opportunities through miniaturization and multilayering of interconnect layers in the logic field

# **Semiconductor and Memory Growth Roadmap**

#### **Technology Trends**

Progress in miniaturization

Acceleration of 3D structures

Introduction of new materials

#### **Our strengths**

Low-particle film deposition

Stress control

High-density film formation

#### Growth roadmap

#### **CVD** and **ALD** integration

Under development with leading memory manufacturers

Development of new materials and low-resistance film deposition technologies, and expansion of mid-process wiring

Proven track record

Cu bonding

**New Materials**

Expansion of cutting-edge memory processes such as metal film processes and HM processes. and customer expansion

# Mid- to Long-Term Goals

# Maximizing market share in memory processes

- Accelerated joint development with a leading Korean manufacturer to expand the number of processes (utilizing the Technology Center)

- Expansion of processes through the provision of solutions compatible with new materials and structures

# **Sputtering Technology for Metal Interconnect Processes - Memory**

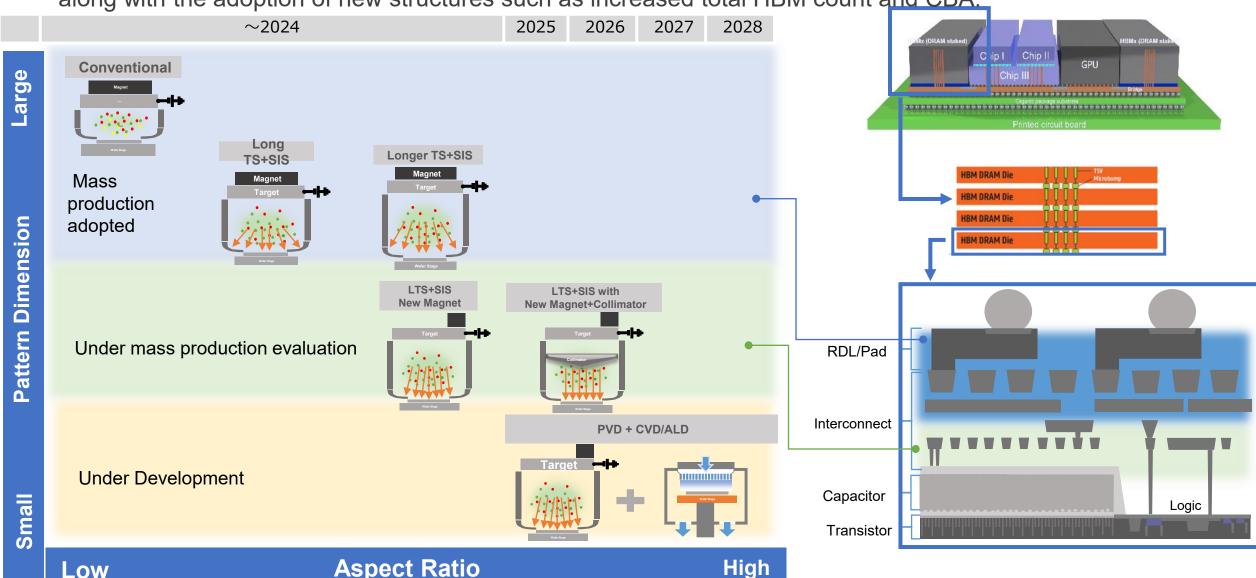

Increased opportunities due to miniaturization and multilayering of interconnect layers in the memory field, along with the adoption of new structures such as increased total HBM count and CBA.

### Participation in the Imec Program and Future Collaboration

- We have participated in the program of Imec, a leading semiconductor research and development institute based in Belgium.

- By leveraging Imec's expertise and development infrastructure, we aim to accelerate the advancement of next-generation and beyond semiconductor devices.

# mec

# ULVAC

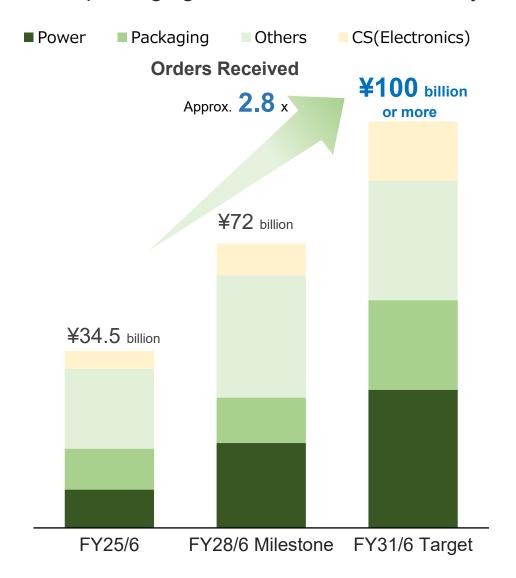

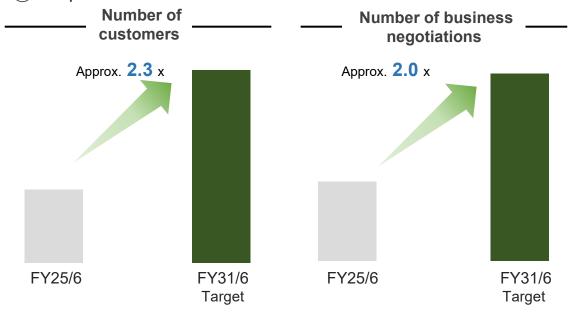

#### **Growth Strategy: Semiconductor Growth Scenario**

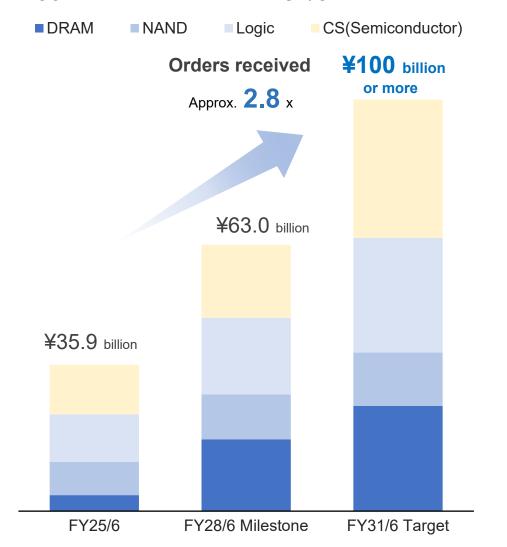

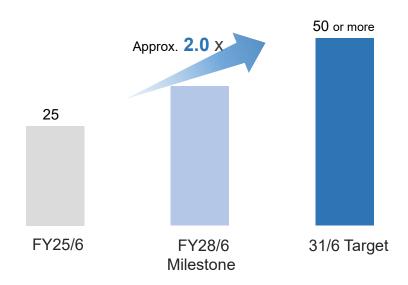

Based on proven hard mask technology and metal film deposition technology, we will increase the number of POR\*s for important customers and expand our market share by acquiring new processes, aiming for orders of ¥100 billion or more in FY31/6.

#### **Growth Strategy**

- Apply HM (Hard Mask) technology to high-density functional films.

- 2 Establish a top position in HM processes and expand into Cu wiring applications.

- 3 Expand PVD market share by securing advanced logic Cu wiring and post-Cu wiring processes.

- (4) Expand and deepen the CS (Customer Support) business.

#### Number of important customers POR

<sup>\*</sup> Process of Record: Certified process used in mass production

# New Initiatives in Advanced Packaging

Harunori Iwai, Senior Executive Officer Junya Kubo, Sales Department 2 Semiconductor and Advanced Electronics Business HQ

#### **Growth Strategy: Growth Scenario for Electronic Devices**

We aim to expand to a business scale of over ¥100 billion and further growth mainly through the revitalization of the packaging business and the recovery of power device investments.

#### **Growth Strategy**

- 1 Expand applications to support GaN mass production in addition to SiC sputtering and ion implantation.

- Capture new processes and benefit from increased investment in advanced packaging.

- ③ Develop optoelectronic fusion businesses through mass production of TFLN (Thin Film Lithium Niobate) etching, contributing to the miniaturization of communication devices.

- 4) Expand and deepen the CS business.

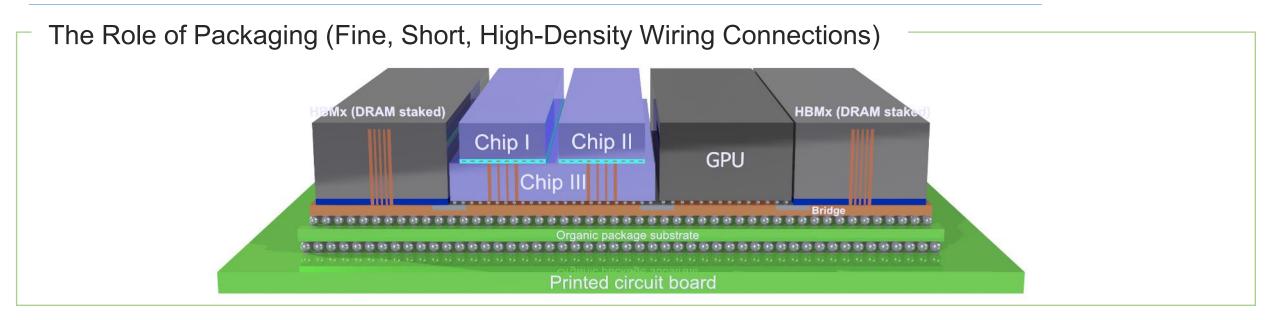

- 1. Advanced Packaging

- 2. Surface Treatment Technologies used in Advanced Packaging

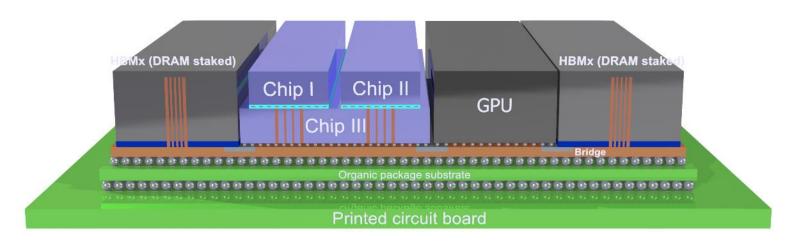

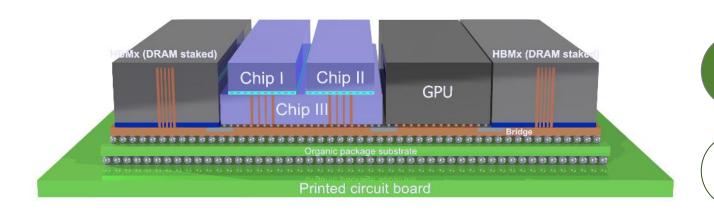

# Essential Elements for Packaging Required in Al Semiconductors **ULVAC**

## The Role and Technological Evolution of Advanced Packaging

## Our Technologies Utilized in Advanced Semiconductor Packaging ULVAC

Desmear Processing for Interposers

Desmear processing for packaging substrates

Etching for glass processing (optical waveguide formation)

TGV Glass substrate patterning

TSV Etching

Plasma surface activation (hybrid bonding)

Electrode formation sputtering

Seed sputtering for packaging substrates

Etching for fine patterning

Plasma Dicing

**Surface cleaning/hydrophilic treatment**

- 1. Advanced Packaging

- 2. Surface Treatment Technologies used in Advanced Packaging

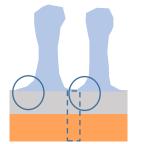

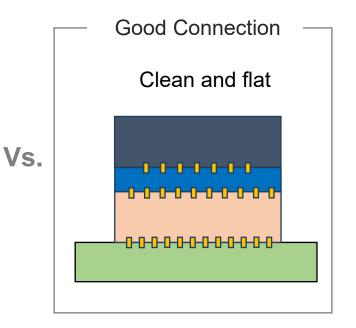

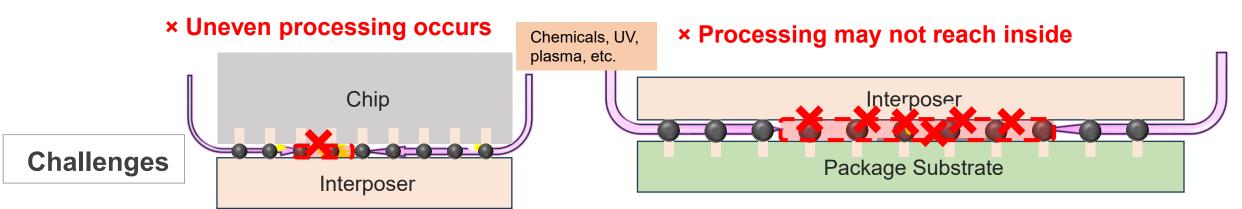

# Key Points for Multilayer Structures in Advanced Packaging

**Key Points for Multilayer Packaging**

Flat Surface

Clean and good adhesion

No degradation

Efficient transfer of heat and electricity

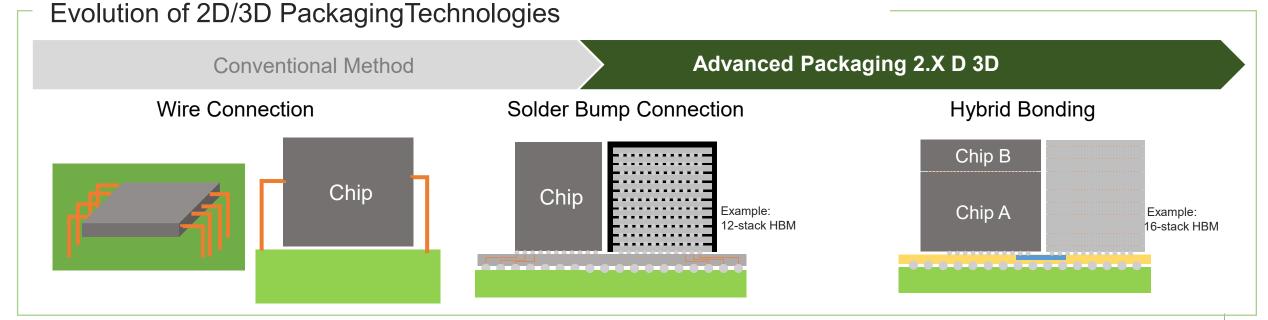

# **Trends in Connection Technology**

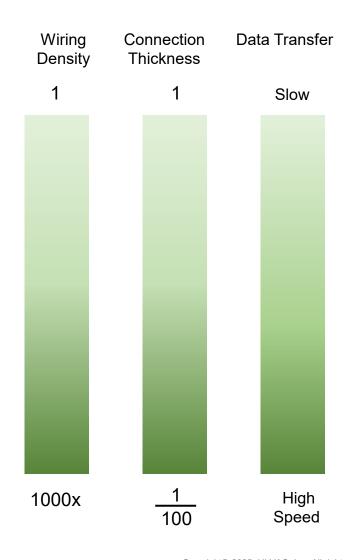

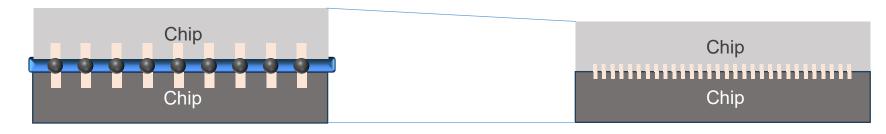

## 3 Methods for Connecting Semiconductors: Smaller, Denser, Thinner

#### Bump

(Application Example) Board Interconnects, High-Current Applications

#### **Micro Bump**

(Application Example) HBM Stacked Memory

# **Hybrid Bonding**

(Application Example) Next-generation HBM, Advanced 3D-IC

# **Trends in Connection Technology**

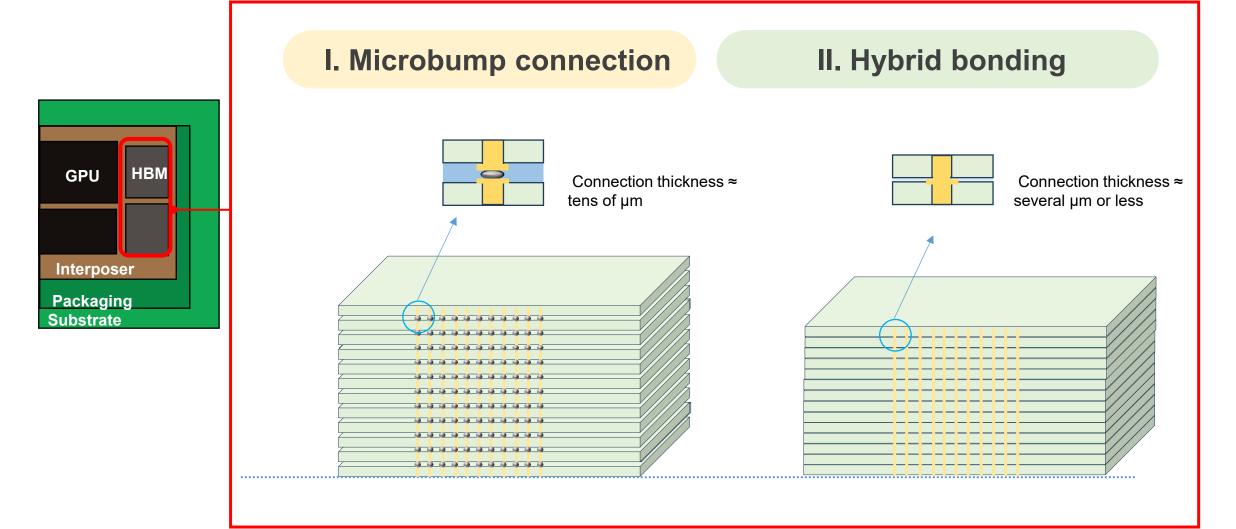

#### **Evolution of Connection Methods in HBM**

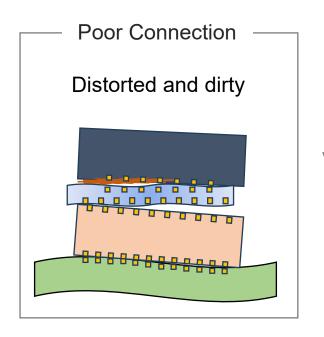

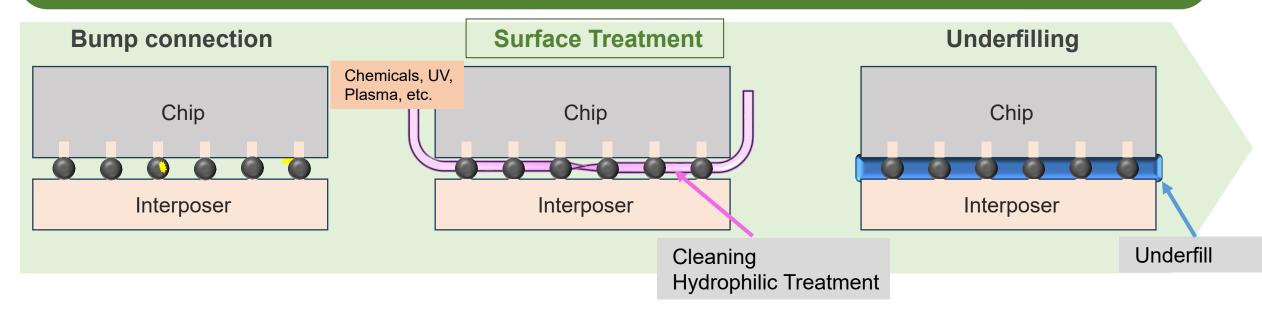

## Surface treatment technologies used in bump connections

# Surface treatment to stabilize bump connections

As chip and substrate gaps narrow and sizes increase in the future,

# **Surface Treatment Technology Used in Bump Connections**

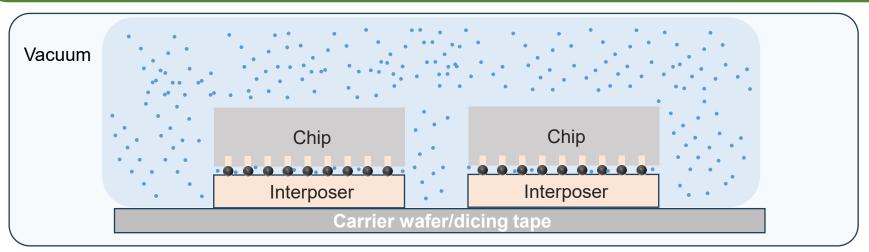

#### **Our Process: Vacuum + Radicals**

Our Process Equipment

Radical: Immediately disappear by highly reactive collide

Vacuum: Maintains radical effectiveness by prevents unnecessary collisions.

## What is hydrophilic treatment?

**Before**

Making the surface water-repellent

After

to a state where water adheres

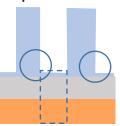

# **Connection Technology: Hybrid Bonding**

## **Hybrid Bonding Applications and Challenges**

#### I. Microbump Connection

#### **II. Hybrid Bonding**

#### **Advantages**

- Increased wiring density

- Thinner due to bump thickness

#### **Challenges**

- High-precision surface treatment and alignment required

- Process optimization for mass production is a challenge

**Expected for application in high- performance semiconductors**

**Expectations for process optimization toward mass production**

Equipment optimization and mass production verification are required for packaging applications

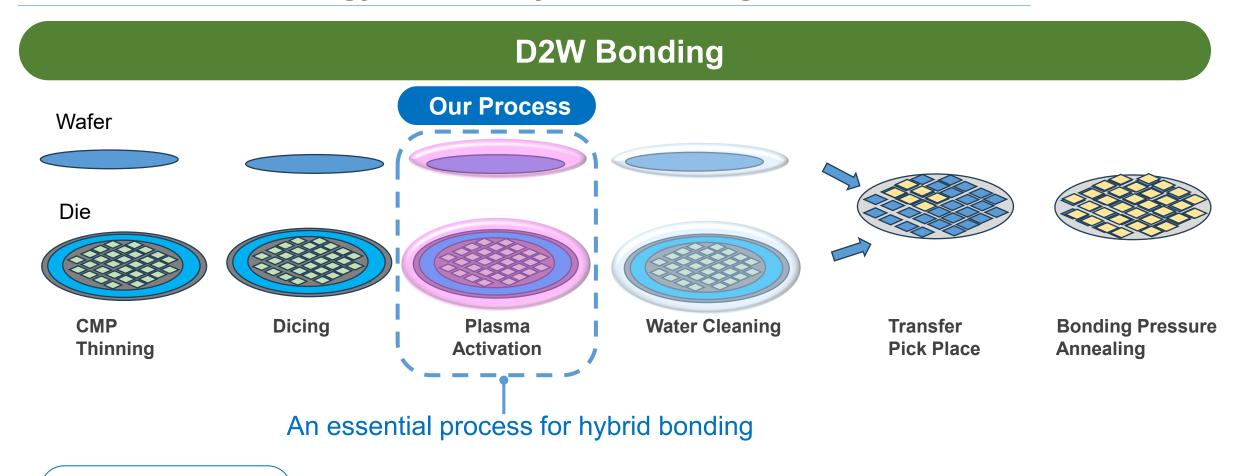

## Activation technology used in hybrid bonding

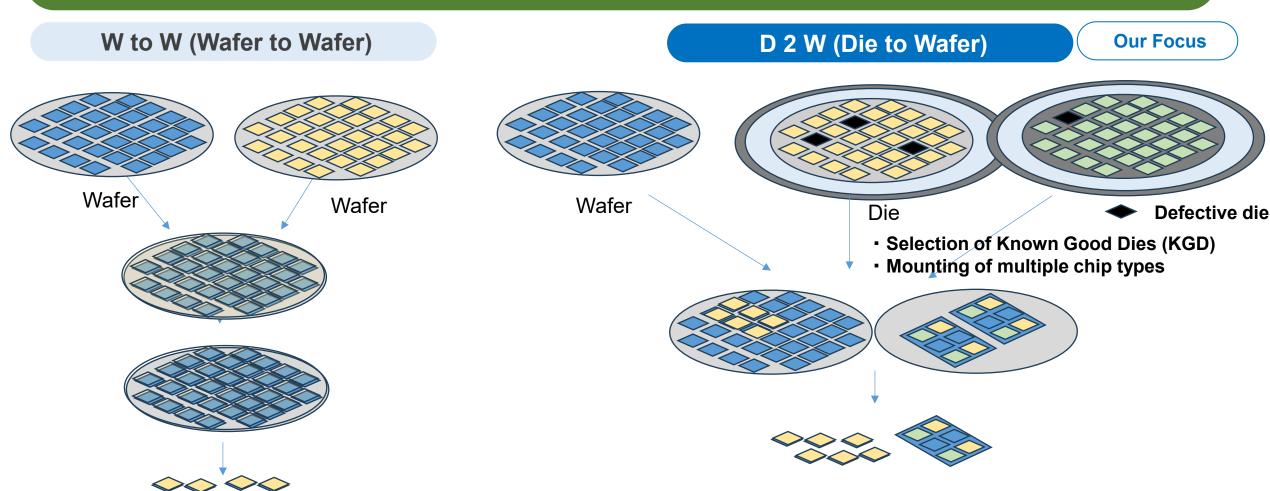

# Types of hybrid bonding

Capable of attaching many chips at high speed Mature and still evolving

Good chip sorting and heterogeneous chip combination possible Mass production development is progressing

## Activation technology used in hybrid bonding

#### **Our Strength**

- Improve substrate surface reaction with using gentle plasma

- Dedicated equipment capable of uniformly processing individual chips

#### Surface Treatment for Advanced Packaging and the Role of Our Equipment ULVAC

#### **Our Advantage for Bump Connection**

**Our Advantage for Hybrid Bonding**

**Smaller Scale**

D2W

Hydrophilicity

Activation

**Dicing Frame Compatibility**

**Dicing Frame Compatibility**

Radical Treatment

Plasma Control

# **Roles of ULVAC**

Optimal Surface Treatment

Stable Equipment Supply

# Strengths and Future Development of Surface Analysis System

Hirohisa Takahashi Executive Officer, President and Representative Director, ULVAC-PHI, Inc. Takuya Miyayama Senior Manager, Product Strategy Department, ULVAC-PHI, Inc.

# **ULVAC-PHI** Corporate Profile Video

#### **ULVAC-PHI**

#### PHI Gr.

- AES Auger Electron Spectroscopy, XPS X-ray Photoelectron Spectroscopy, SIMS Secondary Ion Mass Spectrometry (TOF-SIMS, Q-pole-SIMS) The world's only company possessing all three surface analysis techniques (Hardware, Software)

- A leading surface analysis instrument manufacturer with a strong track record of actual deliveries to national research institutes and top global companies (over 2,000 units delivered, over 1,300 units in operation)

- ULVAC-PHI will leverage its XPS technology cultivated through surface analysis instruments for research and development to challenge the commercialization of XPS inspection equipment for semiconductor mass production lines by FY27/6, aiming to become a world-leading company in both analytical instruments and inspection equipment.

Auger electron spectroscopy (AES)

X-ray photoelectron spectroscopy (XPS)

**PHI GENESIS**

Secondary ion mass spectrometry (TOF-SIMS)

PHI nanoTOF 3+

Secondary ion mass spectrometry (Q-pole-SIMS)

PHI ADEPT1010

#### **ULVAC-PHI**

# **History**

#### May, 1969

PHYSICAL ELECTRONICS (PHI) founded by Dr. R. E. Weber of the University of Minnesota

Developed the world's first commercial AES surface analysis instrument Subsequently added XPS and SIMS to its product lineup, establishing its position as a surface analysis supplier

Founder Dr. R. E. Weber University of Minnesota

#### **April**,1971

Nippon Vacuum Technology Co., Ltd. (now ULVAC, Inc.) signed an exclusive agency agreement with PHI

#### November, 1982

PHI and Nippon Vacuum Technology Co., Ltd. established the joint venture ULVAC-PHI Co., Ltd.

#### February, 2003

Acquired the Surface Analysis System business division from PHI and commenced manufacturing and global sales of surface analysis instruments

#### November, 2023

Established a new company, ULVAC PHI Instruments, in China

#### Present

Operating globally through three companies: ULVAC-PHI (Japan), PHYSICAL ELECTRONICS (U.S.), and ULVAC PHI Instruments (China)

#### **Value Proposition**

Through analytical technologies that "convert the invisible into data and information", we provide critical data and information that supports customers' decision-making.

## **Strengths**

1 Technology featuring high-precision, wide-ranging surface analysis techniques

|                | Surface analysis n competitors       | nethods of                          | ULVAC | Α | В | С | D | E |

|----------------|--------------------------------------|-------------------------------------|-------|---|---|---|---|---|

| Α              | XPS X-ray Photoelectron Spectroscopy |                                     | •     | • | • | • |   |   |

| nalys          | AES Auger electron spectroscopy      |                                     | •     |   |   | • |   |   |

| nalysis Method | SIMS<br>Secondary<br>Ion Mass        | TOF-SIMS<br>Top Surface<br>Analysis |       |   |   |   | • |   |

| d              | Spectrometry                         | D-SIMS<br>Depth<br>Analysis         | •     |   |   |   |   | • |

Excerpt from FY24.6 Q4 Financial Results Disclosure Materials

- 2 Total coordination of analytical instruments

- Hardware: Challenging detection limits

- Software: Converting signals into data and information

- System: Integrated Value Chain

Standard XPS system configuration

35

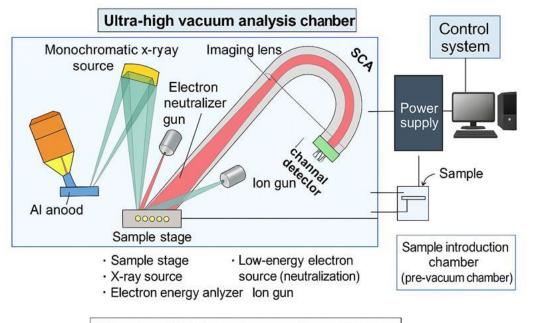

# **Core Technology: What is Surface Analysis**

- Analysis of elemental composition, chemical states, and molecular structure in the surface region at the nanometer scale

- A technique that enables material evaluation by combining two-dimensional distribution observation (imaging) and depth profiling analysis.

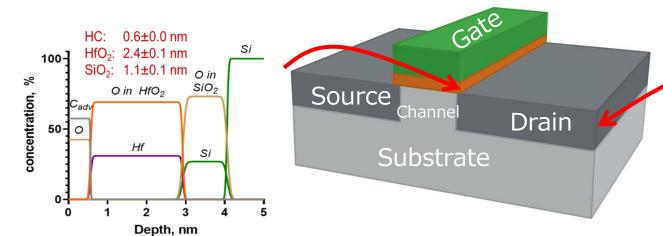

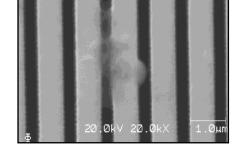

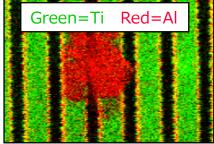

AES (Auger electron spectroscopy) **Excitation** source Electron beam (e-) Detected signal Auger electron **Evaluation of** Measurement content contamination on fine example wiring, etc. Analysis target: few nanometers Auger electron Solid surface Specializes in micro-area analysis similar to electron microscopy

X-rays (Al Kα radiation,etc.)

XPS (X-ray photoelectron spectroscopy)

#### Photoelectron

Evaluation of thin film composition film thickness, etc.

Applicable to both conductive and insulating materials The most versatile surface analysis method

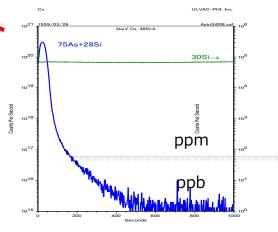

SIMS (Secondary ion mass spectrometry)

Primary ion beam (Cs, O2, Bi, etc.)

#### Secondary ion

Analysis of low-concentration elements, etc.

By detecting ions, trace component analysis at the ppb level is possible.

# Core Technology: Surface Analysis Technology

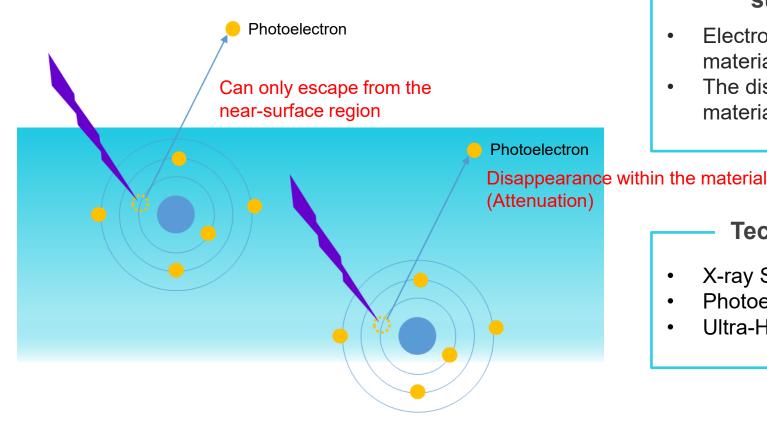

#### **XPS (X-ray Photoelectron Spectroscopy)**

An analytical method that utilizes the photoelectric effect, in which electrons are emitted from a material when it is irradiated with X-rays.

#### The reason why XPS is a surface-sensitive technique

- Electrons lose energy and attenuate within the material.

- The distance electrons can travel within the material is at most a few nanometers.

#### **Technologies Required for XPS**

- X-ray Source

- Photoelectron Analyzer

- Ultra-High Vacuum (Ulvac's Core Technology)

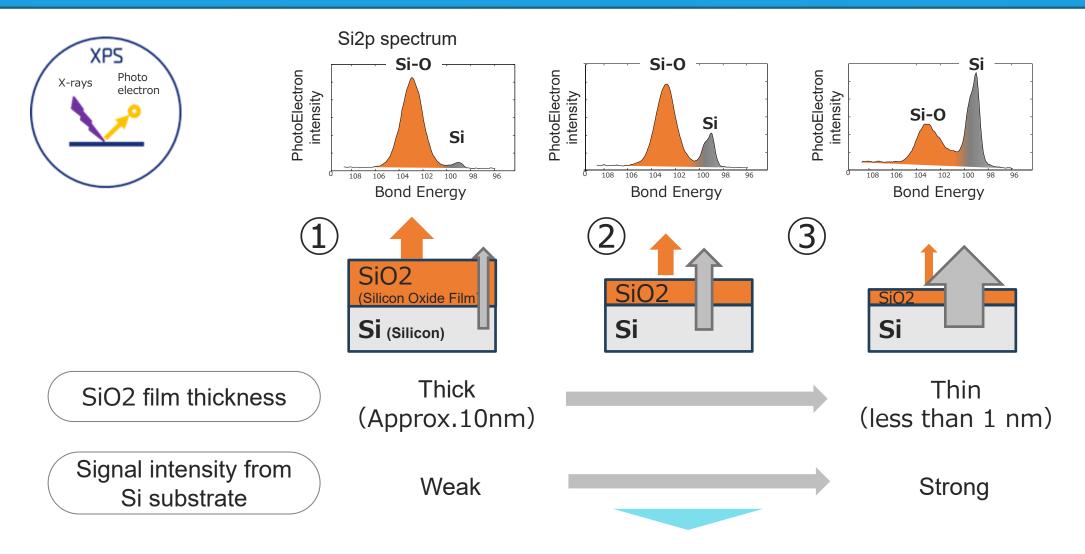

# Benefits of surface analysis: thin film thickness measurement

Thickness evaluation possible for thin films below 10 nm

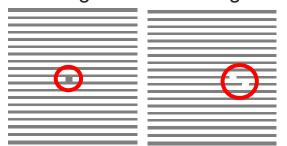

## Surface analysis techniques: essential technologies for semiconductor evaluation

Transistor  $\widehat{\exists}$ Ш 5

#### **XPS**

Non-destructive compositional evaluation of gate oxide film thickness

Film thickness evaluation of a few nanometers

#### SIMS

SIMS

Ion Implanter evaluation for source/drain formation

ppb-level dopant evaluation

Evaluation and measurement of extremely trace amounts of dopants (impurity elements)

#### **AES**

**Contamination/foreign matter evaluation** of the trench area

- ✓ Micro-area analysis similar to electron microscope observation

- Evaluation of contamination/foreign substances on the extreme surface layer

0

ULVAC-PHI, INC. © 2025 ULVAC-PHI, INCORPORATED.

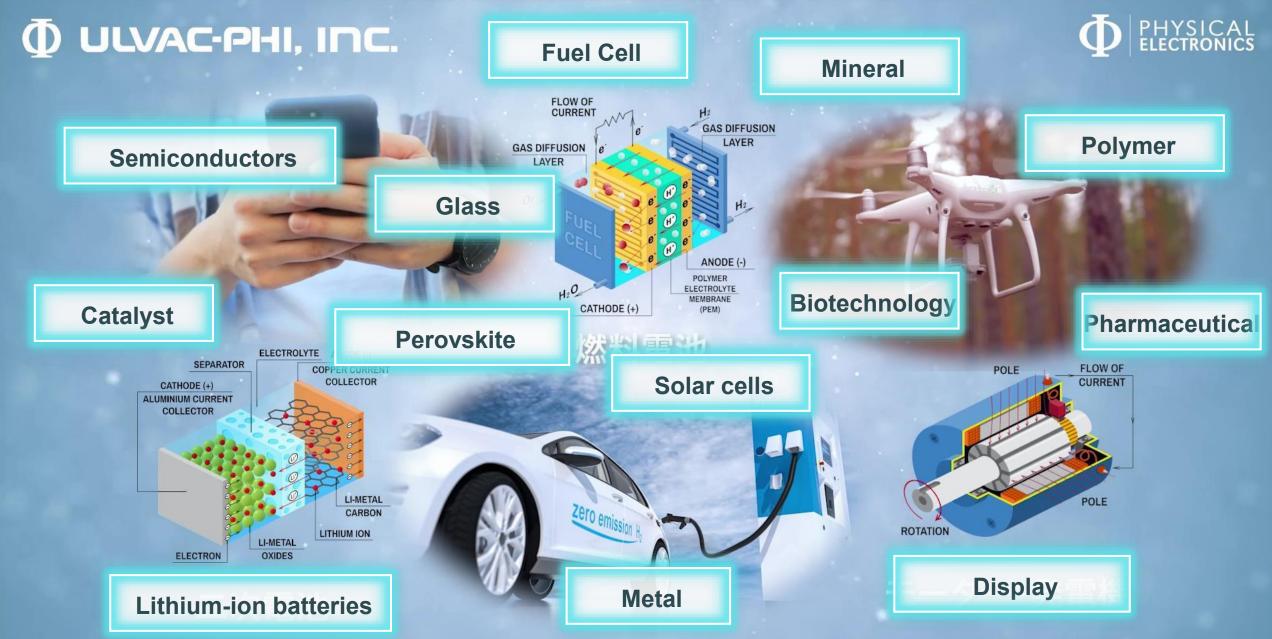

# **Application Fields of Surface Analysis Technology**

#### **Challenge from Lab to Fab**

Leveraging experience and achievements in the existing Lab-type model (market share No. 1), we aim to establish a global position in the inspection equipment market by fully introducing "XPS" into the Fab-type model, where the importance of analysis increases due to the advancement of manufacturing processes, through synergies between semiconductors and electronics and other

#### **Market Environment**

The semiconductor manufacturing process has doubled in the past 10 years, with the inspection process increasing fourfold.

#### by FY25/6

# Top share in XPS analysis equipment for research and development

- Expansion of XPS analysis equipment for research and development

- Prototype development of XPS inspection equipment for semiconductor mass production lines

#### **Technology and Market Trends**

Increase in process steps due to advances in miniaturization

Growing demand for yield improvement

Increased importance of quality control

#### by FY27/6

# Market launch of XPS inspection equipment for semiconductor mass production lines

- Improvement of XPS analysis equipment for research and development

- Product release of XPS inspection equipment for semiconductor mass production lines

Our track record as surface analysis specialist manufacturer

R&D to service integrated system

Providing value from both Software (Science)

/Hardware (Physical and Optical

Design, Manufacturing)

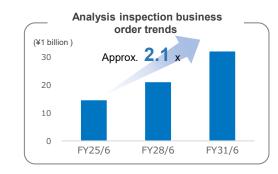

#### by FY31/6

# Aiming for further expansion through scaling global operation Expansion of the lineup of analytical instruments for

- Expansion of the lineup of analytical instruments for research and development

- Expansion of production capacity for XPS inspection equipment for semiconductor mass production lines

- Commercialization of a business generating ¥30 billion in orders for analytical instruments and inspection devices

XPS analysis equipment for research and development

■ EUES UEVACTITI, INCORPORATED.

XPS inspection equipment for semiconductor production lines Image

# **Testing Equipment Analytical Instruments** Takt Time Not specified Required Measurement Target Unknown Known (Materials/Composition) **Measurement Method** Destructive Non-destructive

#### Business Synergy Between Semiconductors and Electronics BU and ULVAC-PHI

We are aiming to realize XPS inspection equipment for semiconductor mass production lines by combining both companies' assets

**ULVAC-PHI**

Surface Analysis Technology (Hardware, Software)

**ULVAC Semiconductors and Electronics Business Division**

Mass production-level handling, low particle, takt time

# **Business Synergy**

XPS Inspection Equipment for Semiconductor Mass Production Lines Release in FY27/6

Aiming for commercialization of a ¥30 billion-scale business in analytical instruments and inspection equipment by FY31/6

Seamless provision of data and information from R&D (analytical instruments) to mass production (inspection equipment) Solutions for production equipment and inspection equipment